It's worth mentioning that these slides are strictly targeted toward AMD's enterprise server chips (EYPC) and aren't focused on its mainstream consumer desktop CPUs.

[...]

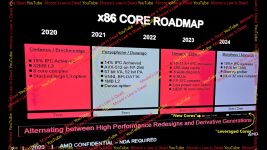

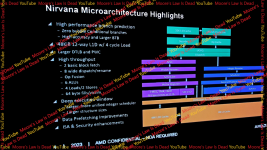

two new allegedly official AMD slides detailing key specifications and IPC targets for Zen 5 and Zen 6. The new slides report that Zen 5 will be a significant architectural overhaul over Zen 4, targeting 10 to 15% IPC improvements or more. Zen 5 will also reportedly incorporate 16 core CCXs for the first time. Before we go much further, we'll need to sprinkle a healthy amount of salt on this report.

The leaked slides also show additional projections regarding AMD's Zen 6 architecture. The slide shows that Zen 6 will have an estimated IPC target of at least 10% at the very minimum, FP16 for AI/machine learning, and a new memory profiler. Finally, the last bullet point mentions that AMD will double core counts again per CCD, jumping from 16 to 32 cores. There's a good chance this second core count doubling will include slower/more compact Zen 6 efficiency cores, but the fact that AMD could be quadrupling core counts in under three generations is impressive nonetheless.